PERCOBAAN 2

DAFTAR ISI

1. Jurnal [kembali]

2. Alat dan Bahan [kembali]

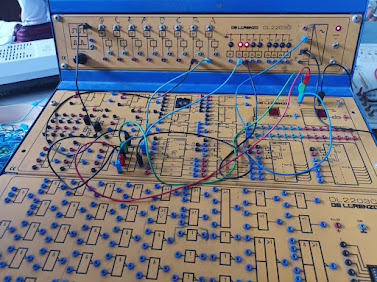

b. Panel DL 2203D

c. Panel DL 2203S

3. Rangkaian Simulasi [kembali]

4. Prinsip Kerja Rangkaian [kembali]

T flip flop adalah kondisi flipflop dikana inputan J-K nya akan digabung menjadi 1. Pada rangkaian T Flip-Flop ini sesuai dengan kodisi yang dipilih yaitu input masukan pada B0=clock yang terhubung ke kaki reset yang diganti dengan clock sehingga R terhubung dengan clock dan B1=1 yang terhubung ke kaki set, maka pada rangkaian ini yang aktif adalah kaki reset karena berlogika 0, yang menandakan aktif low. apabila pada salah satu kaki Reset atau Set berlogika 0, maka untuk kaki J K bagaimanapun kondisinya tidak akan mempengaruhi output. pada rangkaian dapat dilihat bahwa output yang dihasilkan pada kaki Q berlogika 0 dan pada kaki Q' berlogika 1. hal ini merupakan output yang dihasilkan apabila kaki reset aktif.

Apabila pada percobaan, output Q dan Q' menyala secara bergantian maka kondisi itu disebut dengan toggle.

5. Video Simulasi [kembali]

6. Analisa [kembali]

1. Apa yang terjadi jika B1 diganti clock pada kondisi 2?

Jawab :

Saat B0 dan B2 berlogika 0, output Q berubah ubah. Hal ini disebabkan oleh clock yang mengontrol operasi flip flop. Pada keadaan ini rangkaian pada konfisi fall time

2. Bandingkan hasil percobaan dengan teori

Jawab :

Hasil percobaan dengan teori sama, dimana saya membandingkan hasil percobaan (proteus dan alat) dengan tabel kebenaran dari T flip flop

3. Apa fungsi masing masing kaki flip flop yang digunakan

Jawab :

- Input T (digabungkan J dan K : mrngubah keadaan flip flop

• input 0: keadaan flip flop tetap sama

• input 1 : keadaan toggle

- Input clock (clk) : untuk memberikan waktu dan sinkronikasi operasi flip dlop. Keadaan flip flop akan berubah saat clk rendah ke tinggi maupun sebaliknya R dan S : menentukan flip flop dalam kondisi set atau reset

- output Q : output utama flip flop (dipicu oleh input T dan input clock)

- Output Q' : kebalikan dari output Q

- Input

7. Link Download [kembali]

simulasi rangkaian klik disini

Video simulasi klik disini

HTML klik disini

Datasheet T flip-flop (74LS114) klik disini

Datasheet Logicprobe klik disini

Datasheet Switch klik disini

Tidak ada komentar:

Posting Komentar