PERCOBAAN 2

DAFTAR ISI

1. Jurnal [kembali]

2. Alat dan Bahan [kembali]

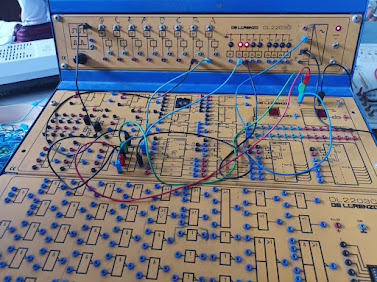

b. Panel DL 2203D

c. Panel DL 2203S

3. Rangkaian Simulasi [kembali]

4. Prinsip Kerja Rangkaian [kembali]

Pada rangkaian percobaan 1 kondisi 3 ini menggunakan 3 jenis IC, diantaranya 74LS90, 7493 dan 74LS47 (IC decoder). Pada IC 74LS90 ni terdapat inputan dari B0,B1,B2,B3 dan IC 7493 inputannya B4 dan B5.

Pada IC 74LS90 ini terdapat 2 inputan clock yang mempengaruhi/mengirimkan sinyal menuju IC 74LS47 yang mana akan merubah output dari IC 74LS90 yang berupa sinyal dan akan diubah ke dalam bentuk inputan digital yang akan masuk menuju input seven common anoda segment, yang mana seven common anoda segment pada anodanya di sambungkan dengan resistor dengan Vcc. Tiap saklar yang di hidupkan atau berubah inputan 1/0 akan mempengaruhi output pada IC 74LS90, lalu akan menuju input seven common anoda segment dan akan di ubah sesuai sinyal/input yang masuk, dan outputnya akan berupa angka pada seven common anoda segment.

Pada IC 7493 memiliki perbedaan dengan 74LS90, dimana apabila salah satu saklar yang dihidupkan maka pada output IC 7493 akan berlogika 1 pada kedua output Q nya. Pada seven segment akan menampilkan angka sesuai dengan inputan yang diterimanya.

5. Video Simulasi [kembali]

6. Analisa [kembali]

1. Jelaskan perbedaan percobaan 2a dan 2b

jawab :

Perbedaan antara kedua percobaan ini dapat dilihat dari rangkaia dan hasil saat rangkaian dijalankan. Dimana untuk input clock B dihubungkan langsung dengan output QA (pada rangkaian percobaan 2b). dan pada outputnya dipercobaan 2a itu counting up namun acak dan pada percobaan 2b itu counting up yang berurutan.

2. Mengapa terjadi perbedaan output pada percobaan 2a dan 2b?

Jawab :

Karena pada rangkaian sendiri clock b langsung dihubungkan dengan QA, pada data sheet setelah inputan CK A dan CK B itu terdapat gerbang NAND, sehingga inputannya akan dikalikan diantara kedua inputan namun karena CK B langsung dihubungkan dengan QA, maka nilainya langsung masuk ke QA.

7. Link Download [kembali]

simulasi rangkaian Rangkaian 2A

simulasi rangkaian Rangkaian 2B

Video simulasi klik disini

HTML klik disini

Datasheet J-K flip-flop (IC 74LS112) klik disini

Datasheet IC 74LS447 klik disini

Datasheet Logicprobe klik disini

Datasheet Switch klik disini